文章是胡杨博士在2011 ICS 上发表的,通过他的模拟软件SSDsim 对SSD 的并行和高级命令(advanced commands)的分析得出了一些SSD 设计实现上的建议.之前都苦于没有SSD 比较详细的综述,于是自己凑了和了一篇(之前写过的综述),而这篇文章则似乎更适合作SSD 的综述,讲的很清晰。

Idea

通过多层次的SSD 仿真器SSDsim 分析了SSD 内部影响性能的因素(并行)。

总结

- large pages 在许多情况下对SSD 有比较大的负面影响

- 越大的pages 更易导致数据的迁移

- 不同physical-page allocation 可应用于不同环境中,对任意工作负载都会有一个最优方案

- Static allocation 读性能在所有情况下最优

- 高级命令在一些情况下能够改进SSD 性能,但是用不当会适得其反

- 使用高级命令必须带有约束条件才能够提升性能

- SSD 四种并行:channel 层、chip 层、die 层和plane 层并行,它们优先级对性能有影响并和2、3中physical-page allocation 与高级命令相互作用、影响。

- 并行的优先顺序应该为:1、channel-level 2、chip-level 3、die-level 4、plane-level

一、基础知识

下面是SSD(Flash)的一些基础特性,在这里里面也有涉及。

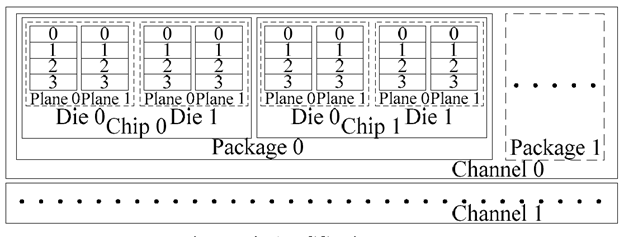

层次结构

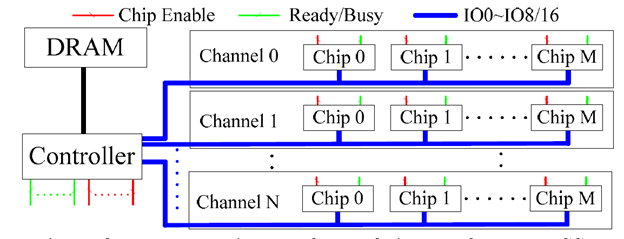

- 首先是包(package)和芯片(chip)的关系,flash 制造商为提高存储密度,将几个芯片打包到一起,共同使用8/16 bits 的数据总线和单独的enable 与 ready/busy 控制信号线。

- 每个芯片会包含两个或者更多碟(dies),每个碟有一个ready/busy 总线,碟会被高级命令使用,但对用户透明。

- 每个碟由多个planes 组成

- 每个plane 由成千个block 组成

- 一个块一般有64 或128 个页(pages),一般NAND flash 的page 大小为512 Bytes

- 页进一步分为子页(sub-pages)512B

chip 和 die

技术进步使单个chip 的容量越来越大,而chip 和die 在之前的文献中也经常混淆。chip 区别于die 重要特性就是有enable 和ready/busy 信号线。一个chip 是最基本的功能单位并具有芯片enable 和ready/busy 信号线。die 是chip 的元件,只有内部的ready/busy 信号线。

两个特征

擦后写:write-after-erase 指的是一次写操作只能够将比特位‘1’变为‘0’,一旦一个page 写入了数据,必须先擦除该页(全部比特位变为1)才能够写入数据。擦除次数:每个比特位的写入次数是有限次数的。MLC flash 次数在10K,SLC flash 次数在100K(假设512Byte 1bit校验)。对于擦除存在一个限制,我们成为Restriction(a):在一个block 内,pages 的擦除顺序必须顺序的擦除,而不能随机擦除(这个性质就决定了SSD 按块擦除,按页读写的特性)。

Flash 命令

包括三个基础命令:读、编程(program or write)和擦除(erase)。常见的文章中讨论的高级命令也有三个:copy-back、multi-plane 和interleave,下面分别说明:

- Copy-back:同一个plane 中一个page 复制到另一个page 而不占用I/O 总线。但要求该命令的源page 和目标page 同奇同偶(Restriction(b))

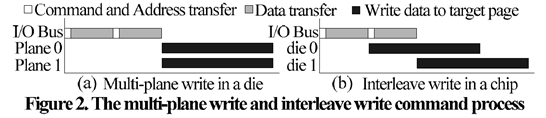

- Multi-plane:同一die 所有planes 进行读、program 或者擦除操作,这里存在第三个限制Restriction(c):这个命令的对应的plane 地址必须具有相同的chip、die 、block 和page 地址,这就是说只能从同一个die 的不同plane 的相同序号的block 才能执行这个命令

- Interleave:同一块芯片不同dies 上同时执行多个pages 的读/写/擦除和multi-plane 读/写/擦除操作(不是很明白,我的理解是可以对同chip 不同dies 进行读写/擦/除和multi-planes 操作)。Interleave command executes several page read, page write, block erase and multi-plane read/write/erase operations in different dies of the same chip simultaneously.

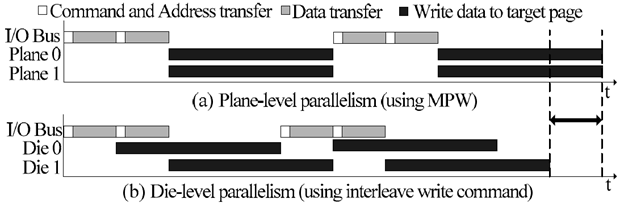

如Figure 2(a) Multi-plane 操作必须在同一个die 中两个planes 同时操作,而Figure(b) Interleave 命令则没有这个约束。

Allocation scheme

Allocation scheme 是指如何选择一个空的page 存放写入到SSD 的数据。可以分为static allocation 和dynamic allocation:

- Static allocation:Static allocation first assigns a logical page to a pre-determined channel, package, chip, die and plane, before allocating it to any free physical page of the plane.(我的理解就是有一个固定的公式计算出下一个写入的page 的地址,这个公式可以是顺序的方法,也可以是一个哈希函数。在写入下一个page 之前就知道了这个page 的位置)

- Dynamic allocation:Dynamic allocation assigns a logical page to any free physical page of the entire SSD.(动态分配会根据多个参数来决定page ,比如channel 的空闲等。写入下一个page 之前不知道这个page 会写到哪里!)

SSD 地址

SSD 地址有Full SSD address 和In flash package address。Full SSD address 包括channel+package+chip+die+plane+block+page+In-page,排除了channel 和package 就是In flash package address。

通过下图可以更好的理解SSD 的内部结构和SSD 的并行。

二、SSD 模拟器

SSDsim 是胡杨博士在09年写的一个SSD 的模拟器,和其他模拟器不同的是使用了单线程、多层次结构化设计方式,并实现了上面谈到的三个约束条件(Restriction),这是其他模拟器没有做到的。

研究的动机来自于四个问题(1)flash 的page 大小影响SSD 的性能么?(2)如果选择allocation schemes?(3)高级命令总能够提高SSD 性能么?(4)SSD 中四种并行优先级应该是?

文章比对了SSDsim 和SSD 实际原型在不同应用下的响应时间,并通过控制各个时间参数(Page read to register、page write from register、Block erase 等等)实现对SSD 的仿真。下图是高性能SSD channels 和packages 组织的方式之一。

三、实验评估

对应四点研究动机进行实验:

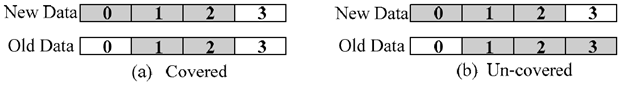

Flash page size

文中讨论了Covered 和Un-covered 两种write 情况,Covered write 所写的数据覆盖了之前的所有数据,所以只需要将新数据写到新的块中,并将旧的块标记为invalidate 即可。而Un-covered write 缩写的数据没有完全覆盖之前的旧数据((b)中 3),于是需要先将旧数据读出,和新的数据组合后写入到新的块,于是多了一个读的操作。

考虑到这点我们可以知道当page 越大,更有可能是Un-covered write 并影响了SSD 性能,因为同样的写在大的page 中更可能是Un-covered write,当然大的page 也有好处,每次读到得数据更多。从实验中可以看出随着page 的增大,Un-covered write 比例明显增加,但响应时间却对不同的应用而不同。

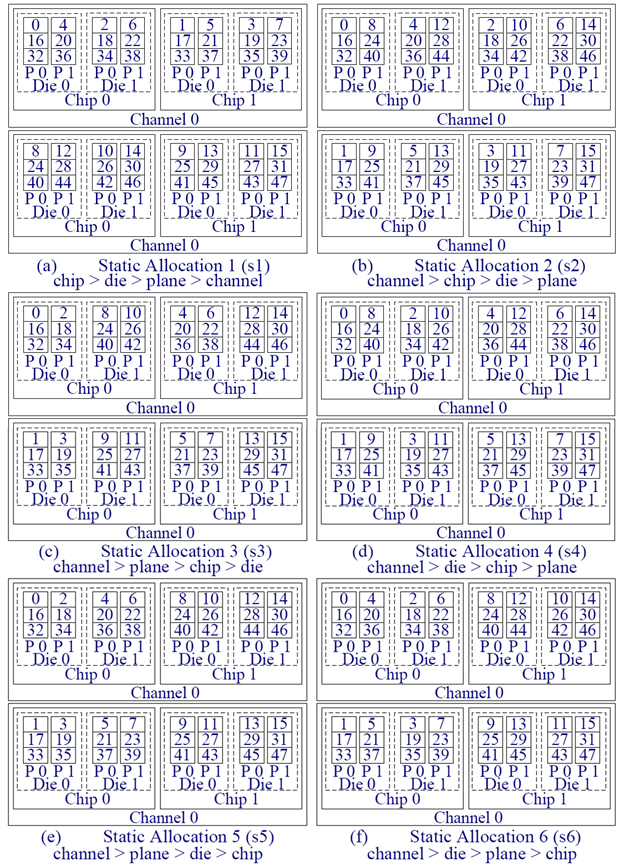

Allocation scheme

在无论新的SSD 或者旧的SSD 中,Static allocation 在任何应用下read 性能都要优于dynamic allocation。 在不同应用的写操作中,dynamic allocation 要普遍优于static allocation。另外许多SSD 采用wear-leveling 算法,将hot data 复制到那些很少被写的块中,以增长SSD 的使用寿命。在wear-leveling 中dynamic allocation 明显要比static allocation 要好,因为dynamic allocation 可以那些不怎么使用的块优先分配。

Advance command

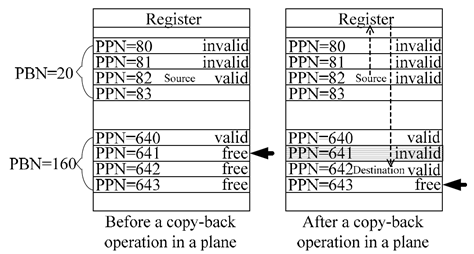

Copy-back 前面谈到了是在同个plane 复制page,并遵循Restriction(a) 和Restriction(b)(连续写和复制页地址相同),如下图从block 地址为20 的PPN=82 页复制到block 地址为160 的块中,因为对应页地址应相同(都是相对偏移3),所以复制到PPN=642 的页中,而因为Restriction(a) program 必须是顺序的,所以PPN=641 的页必须标记为无效页。

所以为了避免这样类似PPN=641 的无效块,我们推荐当目的地址和源地址同奇同偶才执行该命令。试验中也给出了如果该命令没有用好,会导致某些应用中SSD 性能严重下降(MSN)。

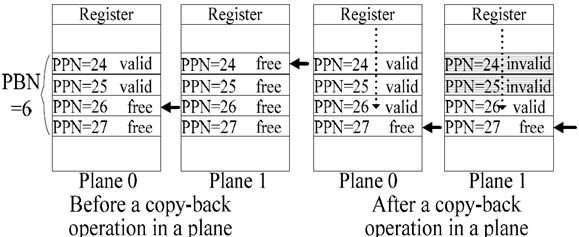

Multi-plane 指可以再同个die 不同plane 执行相同的basic command,并遵循Restriction(a) 和Restriction(c)(连续写和复制不同plane 的chip、die、block 和page 地址都应该相同)。

如上图plane 0 和plane 1 同时进行写,但因为开始的page 不同,所以plane 将前两个pages 标记为无效使得page 地址和plane 0 地址相同后再同时进行写操作。WPW(Multi-Plane Write)可以带来SSD 写性能的提高,但也会有些页面被浪费。和Copy-back 中我们推荐的不同,MPW 很少能遇到不同plane 对应相同的page 要写,所以做类似Copy-back 的约束对性能不能有很大提升。

Interleave 利用同一块chip 上不同dies 的并行提高性能,并对SSD 寿命没有影响。

最后综合三种命令发现:use the copy-back wisely、the MPW blindly,and the interleave command ubiquitously 能达到最好的性能(response time )。

parallelism

前面也谈到了SSD 有四层并行:channel、chip、die 和plane 层,那它们的优先级应该是怎么样的呢?文中给出的顺序是:1、the channel-level parallelism 2、the die-level parallelism 3、the plane-level parallelism 4、the chip-level parallelism。对照下图可能更清楚些了。

对比 (b)、(d) 只在die parallelism 和plane parallelism 不同,而(d) 中die parallelism 可以利用同块chip 不同dies 的并行读写,所以die 的并行应该在chip 并行之前,毕竟跨chip 的读写还是很少的。

对比 (e)、(f) 只在plane parallelism 和die parallelsim 不同,而(f) 可以利用interleave 写,而(e) 只能使用MPW 造成多余的擦除操作,所以die 并行应该在plane 并行之前。

对比 (d)、(e) ,(e) 要优于 (d),这是因为(d) 在请求四个blocks 会因为interleave 命令使得两块chips (我感觉应该是两个die,比如读0-3,会使得chip 0 的die 0 和die 1都busy )都处于busy,而(e) 只需要一个interleave multi-plane 即可,chip 0 的die 1 将不会处于busy。因此chip 并行优先级应低于plane 并行。

考虑plane parallelism 和die parallelism 也可以下图即可明白:

至此结束。文中结论均在文中给出。读后对interlevel 不是很明白